FD-SOI制程

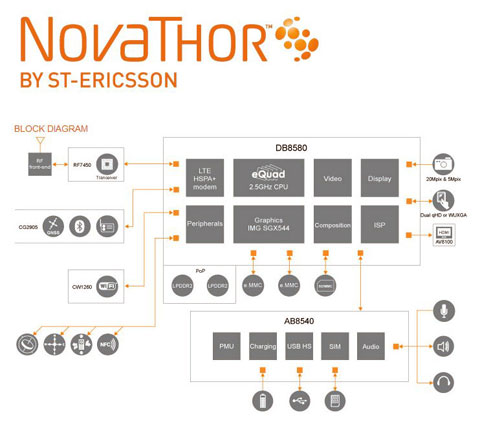

在今月2月下旬的MWC2013中,ST-Ericsson展出了工作频率达3GHz的NovaThor L8580 ARM处理器,在业界造成轰动。它不但是首个可工作于3GHz的ARM处理器成品,而且它的高频率主要得益于SOI技术。似乎沈寂多年的SOI技术将于在国际舞台上再一次大放异彩。(编按︰去年TSMC生产3GHz ARM Cortex-A9属于试验性质而非面向市场的最终成品)

现有架构产品 提升频率有助制作工艺

ST-Ericsson的3GHz ARM处理器基于ARM成熟的Cortex-A9微架构。此架构也是目前最成功的ARM处理器架构,在性能及功耗方面表现出色。不过应当要指出的是,Cortex-A9并不是一颗高频率设计的处理器,它只有8阶管线(pipeline),不像新一代Cortex-A15采用15阶管线的高频率设计,一般估计Cortex-A9最高频率为2GHz,若果要提升频率的话,除了对Cortex-A9微架构进行有限的改良外,只有从制作工艺方面入手,这也是ST-Ericsson NovaThor L8580 处理器的选择,采用了FD-SOI制程以提升频率。

突破3GHz的NovaThor L8580 ARM处理器,共整合了4核Cortex-A9。

从IBM专利技术到SOI工业协会

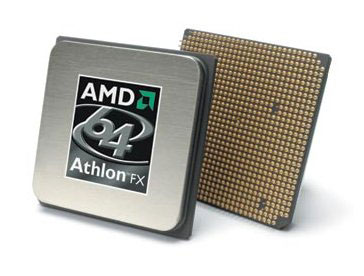

现在回头再谈谈SOI技术。SOI技术大家对它并不陌生,此技术在1998年由IBM推出,原理是在硅晶体管之间加入绝缘体物质,可减少寄生及电流漏电。据IBM方面表示,SOI技术可以提升30%的芯片性能,减少5-7倍的电流漏电及减少25%芯片面积的可能。第一款应用SOI技术处理器是IBM为Apple Mac计算机生产的PowerPC G4处理器(由Motorola设计,IBM有份生产),其后AMD在K8处理器引入SOI技术,在制作工艺上与Intel平分春色,最为人津津乐道的是90nm制程之争,Intel Prescott Pentium 4电流漏电问题严重,而AMD却很好地控制了功耗,当中SOI起了很重要的作用。目前除IBM及Global Founderies (AMD分拆的工厂业务)外,积极研发SOI技术还有Motorola、德州仪器及NEC等厂商。在2007年,IBM更主导了SOI工业协会(Industry Consortium,网址︰www.soiconsortium.org),成员包括业界领导的公司、学院及研发机讲,拥有包括AMD、ARM、IBM、NVIDIA、TSMC、Samsung及ST等等业界巨擘在内共26个会员。

对于SOI技术,也有厂商视之为过渡性技术,如Intel便一直拒绝SOI。Intel认为SOI技术需要硅晶体管之间加入绝缘体物质,制作颇为复杂,而且只能解决一时的问题而非全面性的方案。为此Intel提出采用High-K Metal-Gate电介质方案,表示可有效地解决电流漏电的问题,更率先在45nm制程引入High-K Metal-Gate技术,而半导体技术进入32nm年代后,更几乎都采用了High-K Metal-Gate技术,那么SOI技术是否没有需要,被时代所淘汰呢?

AMD在K8中引入SOI技术,在当时曾引起热烈的讨论。

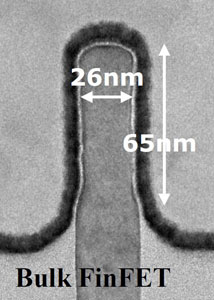

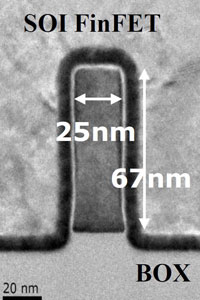

比较Bulk FinFET与SOI FinFET在电子显微镜的效果,可见SOI加入了绝缘层。

从PD-SOI到FD-SOI

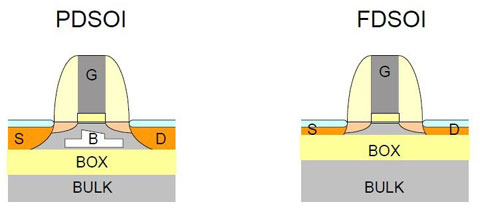

SOI技术是否会被淘汰呢?这要看SOI技术能否自我完善,与时并进推出尖端的性能。而SOI自推出的那天即不断作出改良,在45nm时已达第6代SOI技术,目前SOI制作更因应绝缘体上硅膜厚度的不同分为薄膜部份耗尽(Partial Depleted, 简称PD-SOI)以及薄膜全耗尽(Full Depleted, 简称FD-SOI)结讲,以下是两款的横切面图︰

图中左方是PD-SOI,右方是FD-SOI,可以见到PD-SOI并没有完全覆盖P通过,因为FD-SOI采用标准尺寸的硅膜(如145nm),需要制作简易但无法有效阻隔电离的流出。图中可见大量电离从绝缘体中流出,并形成区域“B”的“quasi-neutral region”,带来浮体效应(floating body effect),导致寄生电容及产生电流漏电等不良影响。事实上,PD-SOI属于早期的技术,主要针对180nm至22nm半导体制作工艺,而进入28nm、22nm时代,厂商开始提倡更先进的FD-SOI工艺,特点是引入超薄的硅膜(10nm或25nm),可有效阻隔电离,所以没有浮体效应的问题。FD-SOI另一特点是因为采用了超薄的硅膜,所以能满足缩小制程的需要,现阶段已规划了14nm以及10nm制程的版本了,相反PD-SOI未来要缩小制程将遇到物理的限制,无法延续摩尔定律(Moore’s Law)要求的技术进步。但PD-SOI技术成熟,况且市场上已有大量PD-SOI制作设备所以生产成本较低,令其在短时间内无法为FD-SOI所取代。

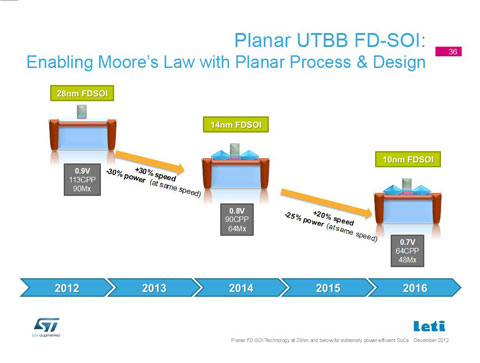

目前FD-SOI已规划了下一代的14nm以至下下代的10nm FD-SOI制程。

FD-SOI技术的优势

现在再看看采用ST-Ericsson在采用FD-SOI技术后,对所生产的ARM处理器带来甚么技术优势呢?据ST-Ericssion表示,FD-SOI加入buried oxide layer的簿绝缘体层,可减少硅晶Channel加入掺杂物的需要,可提供绝佳的短沟道控制(Short Channel Control)性能,而且使背栅控制(Back Gate control)变得可能,而且FD-SOI可限制核心厚片,有助缩小晶圆尺寸。这些技术最终为消费者带来尺寸更小、功耗更低及更高频率的CPU。

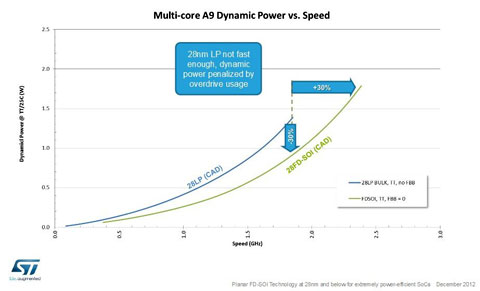

ST-Ericsson表示,由于采用了28nm FD-SOI工艺,比28nm Bulk CMOS最多可减少达2倍的漏电值。他们以1.00V Vdd为例,此时28nm LP IDDQ a.u.为1,而FD-SOI为0.61,有39%的差距,而考虑到FD-SOI不影响性能下可以0.85V工作,此时FD-SOI为0.39,相当于有2倍的漏电值差距。减少漏电值的好处,可用以提升30%以上的CPU工作频率,或减少50%的功耗。这些性能用作提升频率的话,是使NovaThor L858可以工作在3GHz的高频率;若果用于降低功耗的话,是容许NovaThor L8580在不影响性能的前提下于0.6V低电压工作,比一般Bulk CMOS节省50%的供电。

ST-Ericsson研究所得,同为Cortex-A9 MP架构下,FD-SOI比28nm LP带来30%以上的频率增长。

FD-SOI成本的问题

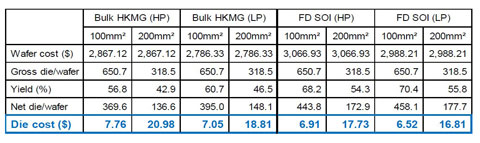

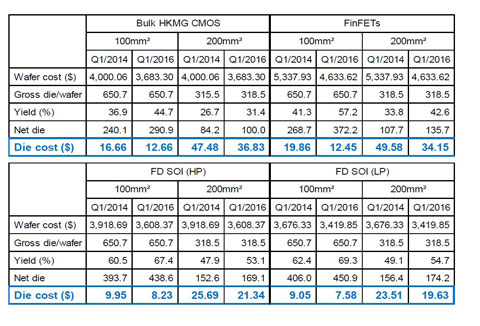

在竞争激烈的市场上,光有好的技术是不足够的,更重要是成本增加需控制在市场能够接受的水平,并且得到足够厂商的支持,这方面由于FD-SOI可以沿用大部份现有的半导体生产设备,有助降低生产成本,至于具体生产成本,IBS公司的创办人及CEO Dr. Handel Jones在题为“经济因素在28nm/20nm技术选择上的影响”(Economic Impact of the Technology Choices at 28nm/20nm),比较了28nm与20nm制程下,使用100mm2或200mm2晶圆生产成本。

28nm工艺下的生产成本比较︰

20nm工艺下的生产成本比较︰

总结以上数字,有以下结论︰1. FD-SOI因为要采用SOI工序的晶圆(Wafer),所以生产成本比Bulk HKMG CMOS高,但在20nm相差不大。2. 虽然FD-SOI生产成本较高,但考虑到FD-SOI生产良率(Yield)比Bulk HKMG CMOS高,尤以20nm时为甚,所以反过来FD-SOI的生产成本会较高。不过,厂商实际生产成本往往是图表无法反映得到的。如人员培训的支出,测试的成本,以及为风险拨备的支出等等都会影响到最终的生产成本,并最终影响到厂商是否采用。

除了制作CPU外,SOI工业协会也积极推动FD-SOI在其他方面的应用,如光纤主动线材、Intel的光学 waveguides、高精密度MEMS、数字相机用的CMOS 影像传感器、Multi-GHz RF电路、高集成度Radio、汽车电池用的High-voltage switching以及高性能内存等等。

除了CPU外,FD-SOI还被各个领域所采用。

结论︰声势大不如前的SOI技术

或许是年轻时对SOI技术留下了深刻的印象,所以对于FD-SOI新技术特别感到兴趣。笔者认为,FD-SOI技术虽然带来了30%频率的提升或50%功耗的降低,但半导体技术日新异,SOI技术已不是当前最新颖的技术,今天的3GHz ARM处理器,并不是市场上顶级的CPU,与SOI初初推出时被应用PowerPC G4、K8等先进CPU有天渊之别。